# Technology Related Design of Monolithic Millimeter-Wave Schottky Diode Mixers

Jean-Marie Dieudonné, Bernd Adelseck, *Member, IEEE*, Karl-Ernst Schmegner, *Member, IEEE*,

Rainer Rittmeyer, Alexander Colquhoun, *Member, IEEE*

(*Invited Paper*)

**Abstract**—The development of monolithic millimeter-wave Schottky diode mixers based on technological parameters is described. The complete equivalent circuit of the monolithic Schottky diode is calculated taking into account the semiconductor layer structure and the device geometry. This model has been used in a harmonic balanced software for designing monolithic single balanced mixers. In *V*-band a minimum DSB noise figure of 3.3 dB and a minimum conversion loss of 6 dB have been achieved. In *W*-band a minimum DSB noise figure of 4 dB and a minimum conversion loss of 7 dB have been obtained.

## I. INTRODUCTION

THE DEVELOPMENT of GaAs millimeter-wave MMIC's is a key factor for the low cost, high volume production and size reduction of millimeter-wave systems. Due to the small dimensions in this frequency range, technologies which allow the monolithic integration of different circuit functions on one chip will be of great advantage. First investigations are aimed at developing monolithic integrated circuits such as mixers for applications in receiver front ends.

A new technology which allows the integration of Schottky diodes (mixer, multiplier) and MESFET's (local oscillator, IF amplifier) on the same chip has been developed [1], [2]. Schottky diode mixers are currently employed in the millimeter-wave frequency range because of their superior performances over MESFET mixers. Because of the MMIC configuration it is not possible to tune the diode matching impedances after the circuit realization, hence a precise equivalent circuit of the diode and a careful analysis of the mixer are required.

An accurate model of the Schottky diode based on the technological parameters is presented in the first part of this paper. The second part is devoted to the mixer analysis which is performed by the harmonic balance technique. In the third part several results of realized monolithic millimeter-wave mixers are given. The desired performances have been already achieved by the first pass design.

Manuscript received August 13, 1991; revised March 5, 1992. This work was supported by the German "Ministerium der Verteidigung."

J. M. Dieudonné, B. Adelseck, K. E. Schmegner, and R. Rittmeyer are with Telefunken Systemtechnik, Deutsche Aerospace, D-7900 Ulm, Germany.

A. Colquhoun was with Telefunken Electronic, D-7100, Heilbronn, Germany. He is presently with Daimler-Benz Research Center, D-7900 Ulm, Germany.

IEEE Log Number 9200460.

## II. TECHNOLOGY AND DIODE MODELING

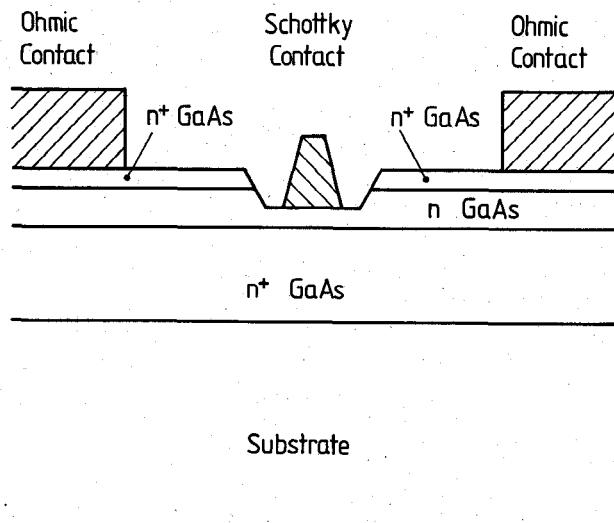

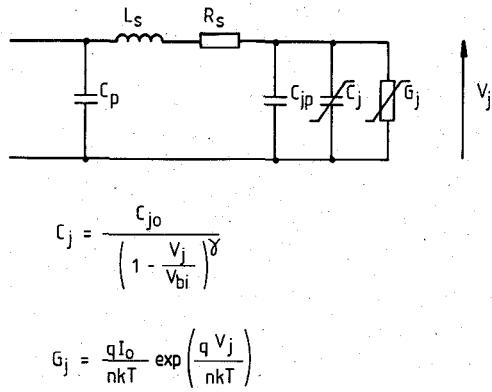

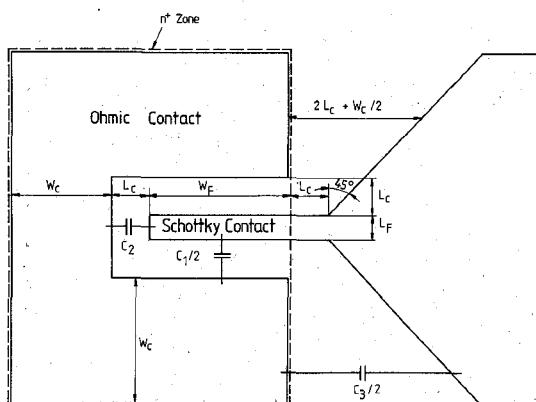

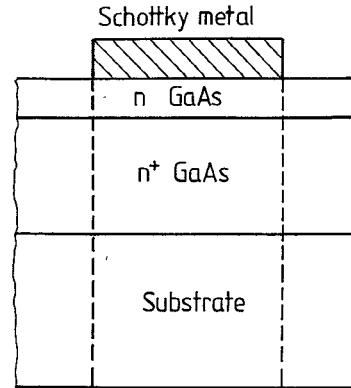

The novel technology for the monolithic integration of both planar Schottky diodes and GaAs MESFET's has been described in a previous paper [2]. It includes an  $n^+$  buried layer to reduce the diode series resistance. A schematic cross section of the planar Schottky diode is shown in Fig. 1. The buried  $n^+$  zones are formed by selective implantation into the semi-insulating substrate. The active  $n$  layer and a further  $n^+$  layer are deposited by MOCVD. The active layer is used for both the MESFETs and the diodes. The gate contact of the MESFETs and the Schottky diode fingers are recessed simultaneously. The minimum structure size is  $0.3 \mu\text{m}$ . A large signal model of the Schottky diode based on the diode structure has been developed. The equivalent circuit shown in Fig. 2 is composed of linear and non linear elements. Each component is described by an analytical equation taking into account the technological parameters. For the calculations the doping profile in the GaAs layers is assumed to be uniform. A top view of a one finger diode is shown in Fig. 3.  $L_F$  is the finger length,  $W_F$  the finger width,  $L_C$  the distance between ohmic and Schottky contacts and  $W_C$  the ohmic contact width. These notations are used in the following model description.

### A. Parasitic Capacitance $C_P$

The parasitic capacitance  $C_P$  is a linear element and represents the coupling capacitance between the ohmic and Schottky contact metallizations. It is composed of four parts:

$$C_P = C_1 + C_2 + C_3 + C_4. \quad (1)$$

The capacitances  $C_1$ ,  $C_2$  and  $C_3$  are given by (2) for two coupled lines after [3]:

$$C_i = \epsilon_0(1 + \epsilon_R)W_i K(\sqrt{1 - k_i^2})/K(k_i) \quad i = 1, 2, 3 \quad (2)$$

where

- $\epsilon_0$  is the permittivity in vacuum

- $\epsilon_R$  is the dielectric constant of the semiconductor material

- $W_i$  is the coupling length

- $K(k_i)$  is the complete elliptic integral of the first kind

Fig. 1. Schematic cross section of the planar Schottky diode.

Fig. 2. Large signal equivalent circuit of the Schottky diode.

Fig. 3. Top view of a one finger diode.

$k_i$  is a parameter depending on the geometry of the coupling lines

In order to consider the corner capacitances at the end of the finger, effective finger coupling lengths have been defined for the finger width  $W_{Fe}$  as  $W_{Fe} = W_F + L_C/2$  and for the finger length  $L_{Fe}$  as  $L_{Fe} = L_F + L_C$ .

$C_1$  is the coupling capacitance along the Schottky finger width. In (2)  $W_1 = 2W_{Fe}$  and  $k_1^2 = L_C/(L_C + L_F)$ ,

$C_2$  is the coupling capacitance at the end of the Schottky finger along the finger length. In (2)  $W_2 = L_{Fe}$  and  $k_2^2 = (2W_C + L_C)L_C/(W_C + L_C)^2$ ,

$C_3$  is the coupling capacitance between the Schottky lead and the ohmic contact (see Fig. 3). In this case a mean gap of  $2L_C + W_C/2$  and a line width of  $W_C + L_C + W_F$  are taken, then in (2)  $W_3 = 2W_C + L_C$  and  $k_3^2 = [2(W_C + L_C + W_F) + (2L_C + W_C/2)] [2L_C + W_C/2]/[(W_C + L_C + W_F) + (2L_C + W_C/2)]^2$ .

The capacitance  $C_4$  in (1) is the parallel plate capacitance between the metallizations of the Schottky and ohmic contacts and is described by the expression (3)

$$C_4 = \epsilon_0 \epsilon_{RP} T_m (2W_{Fe} + L_{Fe})/L_C \quad (3)$$

$\epsilon_{RP}$  is the dielectric constant of the passivation layer  $T_m$  is the thickness of the Schottky metal.

### B. Junction Capacitance

The thickness of the depleted region under the Schottky contact is given by the resolution of the Poisson equation. Assuming abrupt doping densities the parallel plate capacitance  $C_{jpp}$  is expressed by

$$C_{jpp} = (qN_D \epsilon_0 \epsilon_R / 2(V_{bi} - V_j))^{1/2} L_F W_F \quad (4)$$

when the depleted region is only in the n GaAs layer and by

$$C_{jpp} = \epsilon_0 \epsilon_R (2\epsilon_0 \epsilon_R (V_{bi} - V_j) / qN_{DP})^{1/2} L_F W_F + (1 - N_D / N_{DP}) T_n^2)^{-1/2} L_F W_F \quad (5)$$

when the depleted region has reached the n+ buried layer. In (4) and (5)  $N_D$  and  $N_{DP}$  are respectively the doping densities of the n layer and the n+ buried layer,  $V_{bi}$  is the built-in voltage of the Schottky contact,  $V_j$  is the junction voltage,  $T_n$  is the thickness of the GaAs n layer under the contact and q is the electron charge.

The capacitance of small area Schottky diodes is strongly affected by the edge effects. Assuming that the depleted region at the edge of the contact is a quarter of a circle [4], the fringing capacitance  $C_{jF}$  is given by (6).

$$C_{jF} = \pi \epsilon_0 \epsilon_R (2W_F + L_F) / 2 \quad (6)$$

$C_{jF}$  is voltage independent.

The total junction capacitance  $C_{jT}$  is given by

$$C_{jT} = C_{jpp} + C_{jF} \quad (7)$$

In Fig. 2 the total junction capacitance is described by

$$C_{jT} = C_j + C_{jP} \quad (8)$$

with

$$C_j = C_{j0} / (1 - V_j / V_{bi})^\gamma \quad (9)$$

A first solution can be formed by assuming that the depleted region is only in the n layer. In this case

$$C_{jp} = C_{jF}, \quad \gamma = 0.5 \quad \text{and}$$

$$C_{j0} = (qN_D \epsilon_0 \epsilon_R / 2V_{bi})^{1/2} L_F W_F.$$

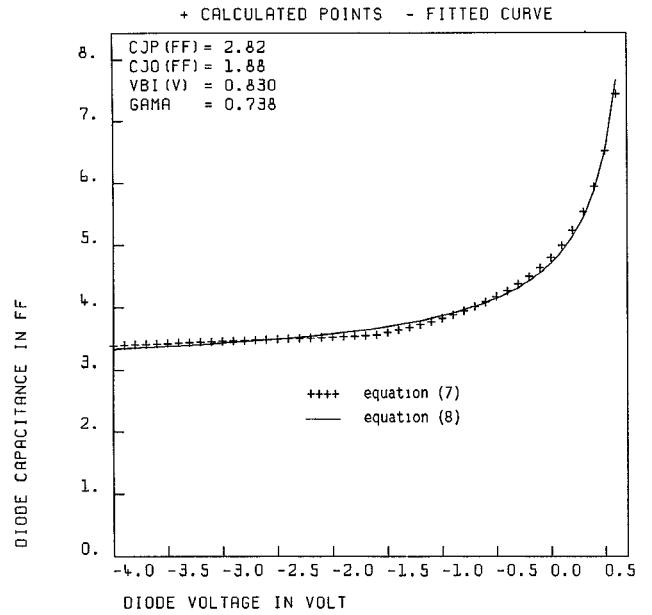

To take into account that the depleted region can reach the n<sup>+</sup> buried layer, the values of  $C_{jp}$ ,  $C_{j0}$  and  $\gamma$  in (8) and (9) have been adjusted to fit (7). An example is given in Fig. 4.

### C. Parasitic Resistance $R_S$

The parasitic resistance  $R_S$  is composed of the ohmic contact resistance  $R_O$ , the resistance between the Schottky and ohmic contacts  $R_{BC}$ , the resistance under the junction  $R_G$  and the resistance of the finger metal  $R_F$ .

$$R_S = R_O + R_{BC} + R_G + R_F. \quad (10)$$

According to [5] the ohmic contact resistance is given by

$$R_O = \sqrt{R'_\square R_C} [\coth(\sqrt{R'_\square / R_C} W_C)] / (2W_{Fe} + L_{Fe}) \quad (11)$$

where

$R'_\square$  is the sheet resistance of the semiconductor layers under the ohmic contact (n<sup>+</sup> ion implanted layer, n active layer and n<sup>+</sup> cap layer) in  $\Omega / \square$

$R_C$  is the specific contact resistance in  $\Omega \text{m}^2$

$W_{Fe}$  and  $L_{Fe}$  are the effective lengths defined in part A of this paragraph.

The resistance between Schottky and ohmic contacts is simply expressed by

$$R_{BC} = R'_\square L_C / (2W_{Fe} + L_{Fe}). \quad (12)$$

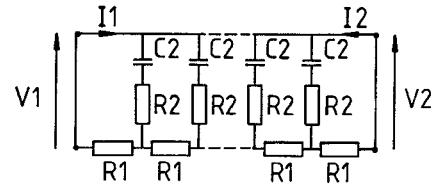

For the computation of the resistance  $R_G$  under the Schottky contact, the distributed network in Fig. 5 is used. The length  $\Delta L_F$  is infinitesimal small:

$$R_1 = \Delta L_F R'_\square / 2W_F \quad (13)$$

is the resistance in the n<sup>+</sup> buried layer ( $R_\square$  is the sheet resistance of this layer)

$$R_2 = \rho (T_n - T_D) / W_F \Delta L_F \quad (14)$$

is the resistance in the n layer where  $T_D$  is the thickness of the depleted region and  $\rho = 1/\text{quN}_D$  is the resistivity of the n layer.

$$C_2 = C_{jpp} \Delta L_F / L_F \quad (15)$$

is the parallel plate capacitance of the depleted region,  $C_{jpp}$  is defined by (4) and (5).

The chain matrix of one cell with length  $\Delta L_F$  is determined and the chain matrix ( $C$ ) of the complete circuit is calculated. The impedance  $Z_G$  under the gate is given by

$$Z_G = V_1 / 2I_1 \quad (16)$$

for  $V_1 = V_2$  and  $I_1 = -I_2$ .

Fig. 4. Calculated junction capacitance versus diode voltage for a  $0.3 \times 5 \mu\text{m}^2$  diode.

Fig. 5. Distributed network model for the calculation of the impedance under the Schottky contact.

From the chain matrix

$$Z_G = C_{12} / 2(C_{11} - 1), \quad (17)$$

$C_{11}$  and  $C_{12}$  are the elements of the chain matrix ( $C$ ).

The resistance  $R_G$  is the real part of the impedance  $Z_G$ .

The resistance  $R_F$  of the Schottky metal is described by the well-known relation [8]

$$R_F = \rho_F W_F / 3L_F T_m \quad (18)$$

where  $\rho_F$  is the resistivity of the metal. The skin effect in the Schottky metal is taken into account by determining

an equivalent thickness  $T_{meq}$  [6]

$$T_{meq} = \delta(1 - \exp(-T_m/\delta)) \quad (19)$$

where  $\delta = 1/\sqrt{\pi\mu\sigma f}$  is the skin depth,  $\mu$  the permeability in vacuum,  $\sigma$  the conductivity and  $f$  the frequency.

The skin effect in the semiconductor is neglected due to the small thickness of the  $n^+$  buried layer ( $0.55 \mu\text{m}$ ) compared to the skin depth. At 100 GHz the skin depth in GaAs layer with a doping density of  $2.10^{18} \text{ cm}^{-3}$  is approximately  $5 \mu\text{m}$ . From the computation the resistance  $R_S$  is voltage dependent. In the model we assume a constant value calculated for a junction voltage equal to zero.

#### D. Junction Conductance

At room temperature the  $I$ - $V$  characteristic of the Schottky junction is well described by the thermionic emission theory [7]:

$$I = I_0(\exp(qV_j/nkT) - 1) \quad (20)$$

$$I_0 = A^* T^2 S \exp(-qV_b/nkT) \quad (21)$$

where

- $I_0$  is the reverse saturation current,

- $A^*$  the modified Richardson constant,

- $V_b$  the barrier height,

- $T$  the temperature,

- $S$  the contact area,

- $n$  the ideality factor.

The junction conductance  $G_j$  is the derivative of the current:

$$G_j = (qI_0/nkT) \exp(qV_j/nkT) \quad (22)$$

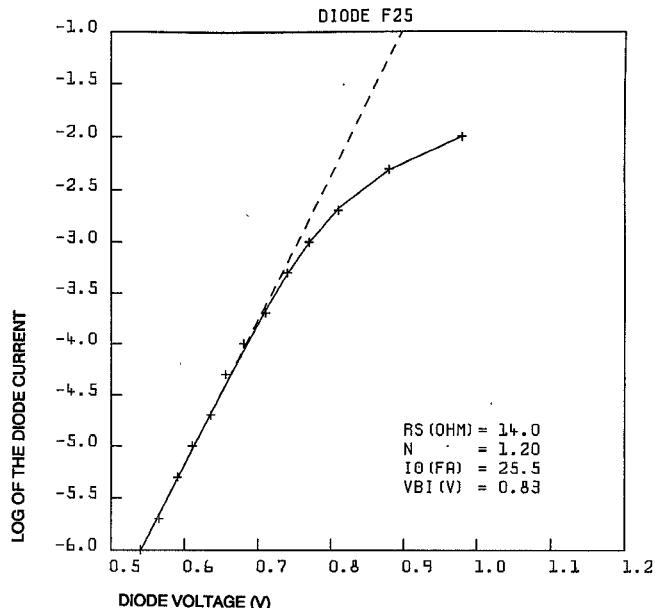

In (22) the ideality factor  $n$  and the reverse saturation current  $I_0$  are to determine. These two parameters are depending on the technology. They can be measured using the characteristic  $\log(I)$  versus the diode voltage as shown in Fig. 6, [8]. The ideality factor is obtained by a linear regression for small current values. The extrapolation of the obtained straight line to a zero diode voltage gives the reverse saturation current  $I_0$ . The dc resistance  $R_S$  is evaluated by the difference between a measured point and the straight line for high current level.

From (21) the knowledge of  $I_0$  allows the evaluation of the barrier height  $V_b$  and then the built-in potential  $V_{bi}$  as

$$V_{bi} = V_b - (kT/q) \ln(N_C/N_D) \quad (23)$$

where  $N_C$  is the density of states in the conduction band of the  $n$  layer. The built-in potential is required for (4), (5), and (9).

For a mature technology the ideality factor and the built-in potential are reproducible, so it is possible to calculate the conductance  $G_j$  of any diode from (22) and (21).

#### E. Parasitic Inductance $L_S$

Due to the planar configuration the parasitic inductance  $L_S$  is assumed to be zero.

Fig. 6. Diode  $I$ - $V$  characteristic. The finger area is  $0.3 \mu\text{m} \times 5 \mu\text{m}$ . + + measurement; ——— slope at low current giving the ideality factor  $n$ ; —— characteristic calculated with the parameters  $R_S$ ,  $n$  and  $I_0$  extracted; from the measurements.

TABLE I

COMPARISON BETWEEN CALCULATED AND MEASURED DIODE SERIES

RESISTANCES AND CAPACITANCES

| Diode Type | Number of Fingers | Finger Dimensions | $R_S$      |          | $C_T$      |          |

|------------|-------------------|-------------------|------------|----------|------------|----------|

|            |                   |                   | Calculated | Measured | Calculated | Measured |

| F01        | 3                 | $0.3 \times 4.0$  | 5.2        | 6.1      | 20.        | 19.      |

| F09        | 3                 | $0.5 \times 4.0$  | 4.7        | 5.0      | 24.        | 22.-26.  |

| F15        | 3                 | $1.0 \times 4.0$  | 4.2        | 3.2      | 35.        | 32.-37.  |

| F25        | 1                 | $0.3 \times 5.0$  | 13.6       | 14.0     | 8.         | 9.       |

Finger dimensions: length  $\times$  width in  $\mu\text{m}$ ;  $R_S$ : diode resistance in ohm;  $C_T$ : diode capacitance in  $f\text{F}$ .

Different diodes have been fabricated and characterized to study the process technology. The measured series resistance  $R_S$  and diode capacitance  $C_T = C_{jT} + C_p$  are in good agreement with the calculated values as shown in Table I.  $C_{jT}$  is defined by (7) or (8) and  $C_p$  by (1). A diode with  $n$  fingers is considered as the parallel connection of  $n$  one finger diodes.

The mean values of the built-in potential  $V_{bi}$  and the ideality factor are found to be  $0.83 \text{ V}$  and  $1.22$ , respectively.

### III. MIXER ANALYSIS

The mixer design is based on the following steps:

- diode nonlinear model using the previous described large signal equivalent circuit;

- harmonic balance analysis of the diode as a single ended mixer to determine the optimum embedding impedances and for the choice of the appropriate diode geometry;

- embedding impedances synthesization;

Fig. 7. Large signal equivalent circuit of the mixer.

complete circuit design (single ended mixer or balanced mixer).

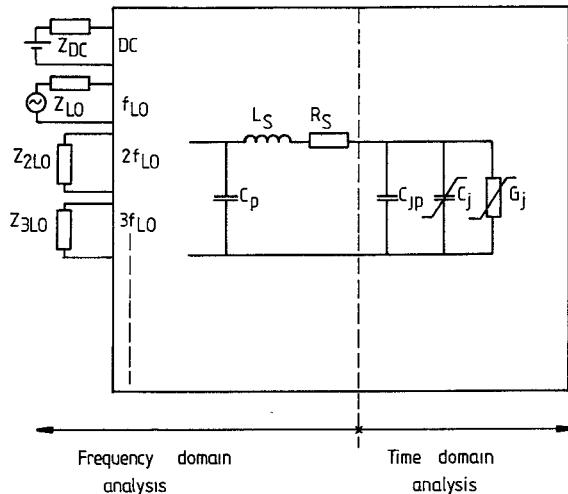

#### A. Single Ended Diode Mixer Analysis

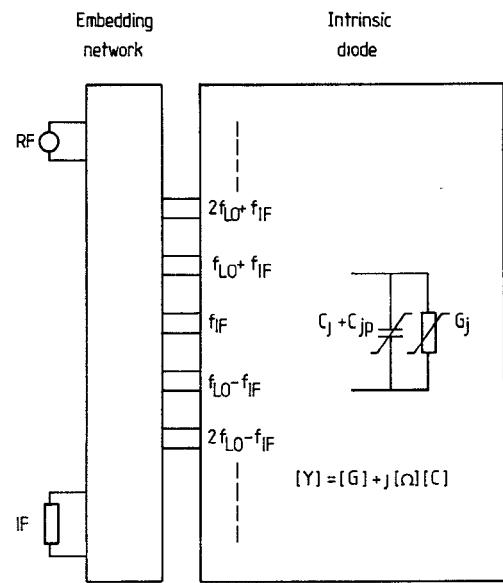

The developed diode model is implemented in a large signal analysis program based on the harmonic balance technique. This CAD program uses the multiple reflection algorithm as described in [9], [10]. The large signal equivalent circuit of the mixer is represented in Fig. 7. It is assumed that the RF excitation is negligibly small compared to the local oscillator so the diode is first analyzed under LO excitation only. The nonlinear elements are treated in the time domain. The parasitic elements and the embedding impedances are analyzed in the frequency domain. So the circuit is divided into a non-linear subcircuit and a linear subcircuit. The voltage waveform at the junction between these two subcircuits is matched to give the same currents in both the time domain analysis and the frequency domain analysis. This time waveforms of the junction capacitance and conductance are formed from the voltage waveform solution of the large signal analysis. The Fourier coefficients of the junction conductance and capacitance are computed for performing the small signal analysis without further consideration of the LO excitation (Fig. 8) [9], [10]. The result is expressed by a multiport conversion matrix considering all sideband frequencies of the form  $n f_{LO} \pm f_{IF}$  with  $n = 1, 2, \dots$ . By taking into account the embedding network this matrix is reduced to a two port conversion matrix with RF and IF signals.

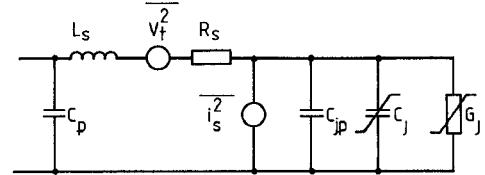

A noise analysis is also implemented in the CAD program. For this purpose the noise equivalent circuit of Fig. 9 is considered [9], [10]. Two noise sources are taken into account:

$\overline{i_s^2}$ : the shot noise due to the junction current depending on the LO waveform;

$\overline{v_t^2}$ : the thermal noise due to the parasitic resistance  $R_S$ .

Fig. 8. Small signal equivalent circuit of the mixer.

Fig. 9. Noise equivalent circuit of the diode. Shot noise source  $\overline{i_s^2} = 2qIB$ . Thermal noise source  $\overline{v_t^2} = 4kT R_S B$ .

The excess noise is not considered. At room temperature it represents a small part of the entire noise [9] but is increasing with the LO power level [11]. For millimeter-wave applications a design goal is to reduce the request of the LO power, so the excess noise can be neglected. Therefore it is possible to simply introduce the excess noise in the thermal noise correlation matrix to derive a complete noise analysis [11].

The CAD analysis program allows the optimization of the RF and image frequency embedding impedances for obtaining the minimum noise figure or the minimum conversion loss.

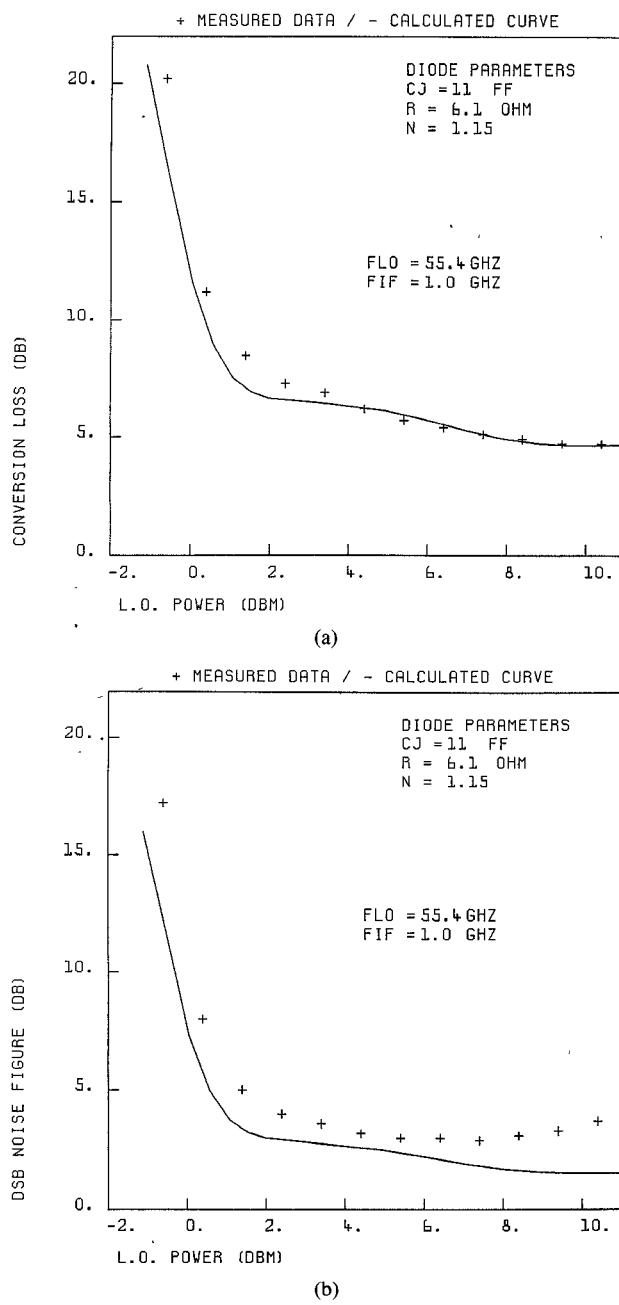

For the validation of the program a hybrid single ended mixer using a 3 fingers diode was realized. Each finger of the diode has an area of  $0.3 \times 4 \mu\text{m}^2$ . The simulated conversion loss is in good agreement with the measured one as shown in Fig. 10(a). The simulated double side band noise figure is slightly lower than the measured one for LO power level under 6 dBm. This can be due to excess noise or AM noise from the local oscillator. For LO power level greater than 6 dBm the excess noise becomes important and the difference between measurement and simulation is greater.

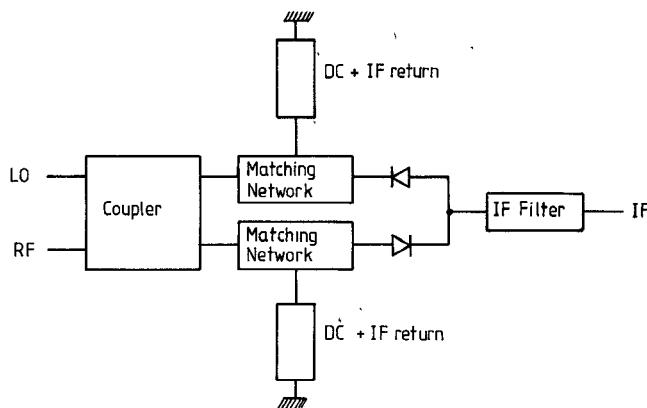

#### B. Balanced Mixer Analysis

An equivalent circuit of a single balanced mixer is represented in Fig. 11. First the Schottky diode is analyzed

Fig. 10. Measurement results of a single ended mixer realized with a 11 fingers diode. (a) Conversion loss. (b) Noise figure.

Fig. 11. Schematic equivalent circuit of a single balanced mixer.

in a single ended mixer configuration as described in part A. The matching impedances for the RF signal and the image frequency are optimized for satisfying the design goal. Knowing these impedances the embedding network of the diode is determined and the complete single balanced mixer circuit is designed. The in house software to calculate microstrip discontinuities and radial stubs has been improved for the millimeter-wave frequency range. A fine linear optimization of the diode matching network is made by considering the entire single balanced mixer circuit. From this analysis the IF impedance can be calculated to realize an optimum matching to an IF amplifier.

#### IV. EXPERIMENTAL RESULTS

We have realized several MMIC single balanced mixers in the *V* and *W*-band frequency ranges. For all these mixers the diode equivalent circuit was calculated from the model described in part II and the mixer analysis was performed as in part III of this paper. Our design goals were minimum noise figure and minimum LO power request. The choice of the diode area was dictated by the power request and the impedance level. The embedding impedances of the RF and image frequencies have been optimized for minimum noise figure.

##### A. *V*-Band Mixer

The results of a first 60 GHz monolithic mixer are reported in [2], [12]. A DSB noise figure of 3.3 dB combined with 6 dB conversion loss in self bias operation has been achieved. The LO power is 6.5 dBm at 55.4 GHz. The IF frequency is 4.1 GHz. The chip area is  $2.5 \times 4 \text{ mm}^2$ . The mixer diode size is only  $0.3 \times 5 \mu\text{m}^2$  in order to drive the mixer with minimum LO power.

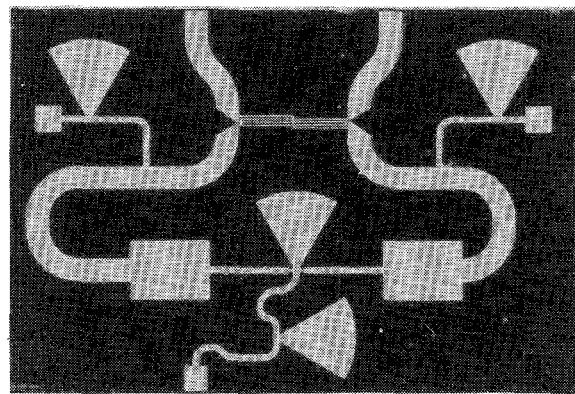

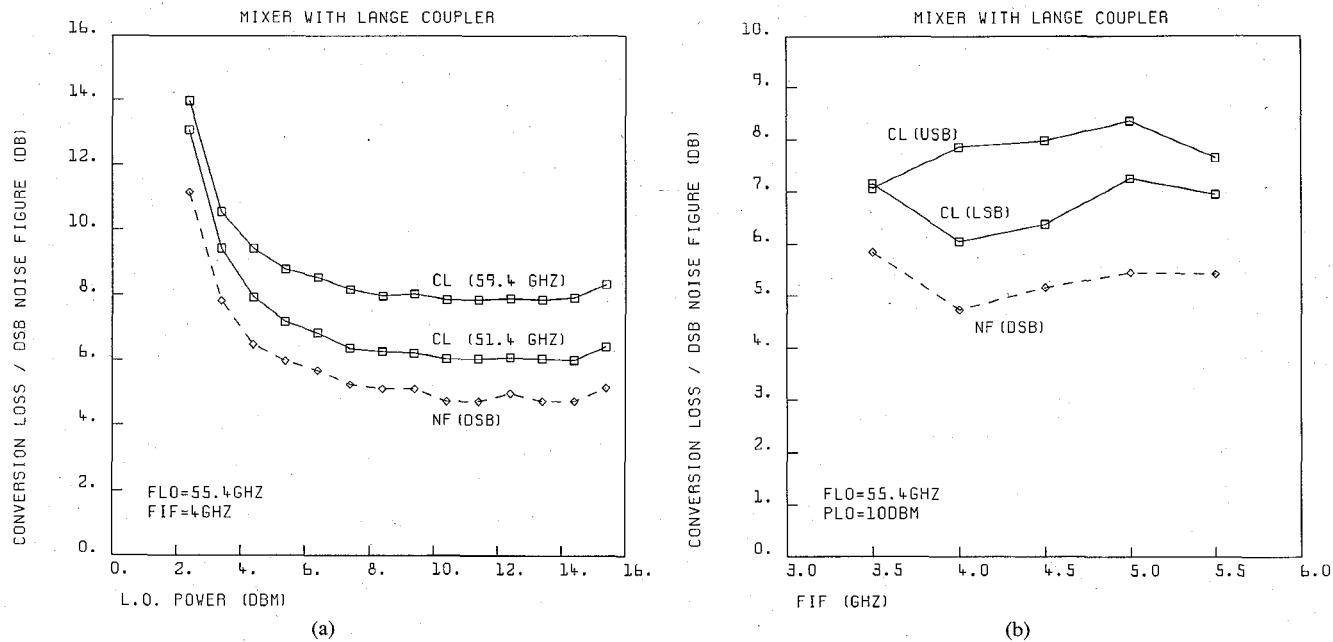

A new mixer for 51 GHz was designed with a Lange coupler. The aim was to reduce the chip area. A diode size of  $0.5 \times 5 \mu\text{m}^2$  was used in this case. The mixer circuit is shown in Fig. 12. The configuration is the same as that of the previous 60 GHz mixer. The mixer is designed for self bias operation. The circuit comprises two via holes for dc and IF returns. The chip area is  $2 \times 3 \text{ mm}^2$ , this is a reduction of 40% compared to the previous mixer. The measured noise figure and conversion loss versus LO power are shown in Fig. 13(a). A DSB noise figure of 4.7 dB associated with a conversion loss of 6.1 dB at 51.4 GHz and 7.9 dB at 59.4 GHz is achieved. The LO power is 10 dBm at 55.4 GHz for these performances. In figure 13b the conversion loss and the DSB noise figure are given for an IF frequency range from 3.5 GHz to 5.5 GHz. In this case the conversion loss is between 7.1 dB and 8.3 dB for the upper sideband and between 6.1 dB and 7.1 dB for the lower sideband whereas the DSB noise figure varies between 4.7 dB and 5.8 dB.

##### B. *W*-Band Mixer

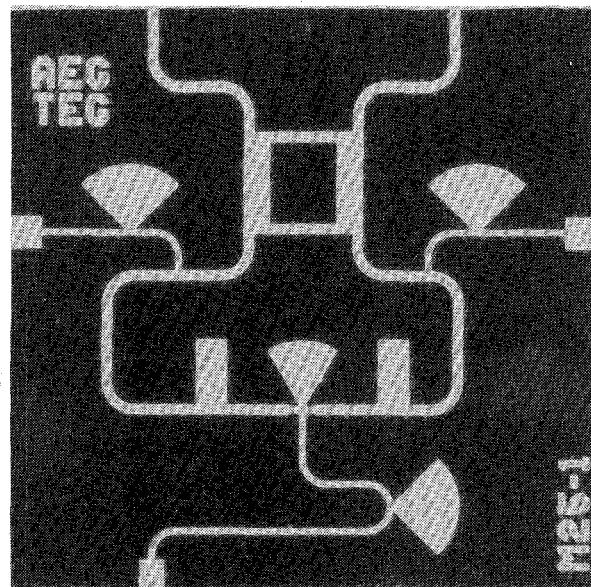

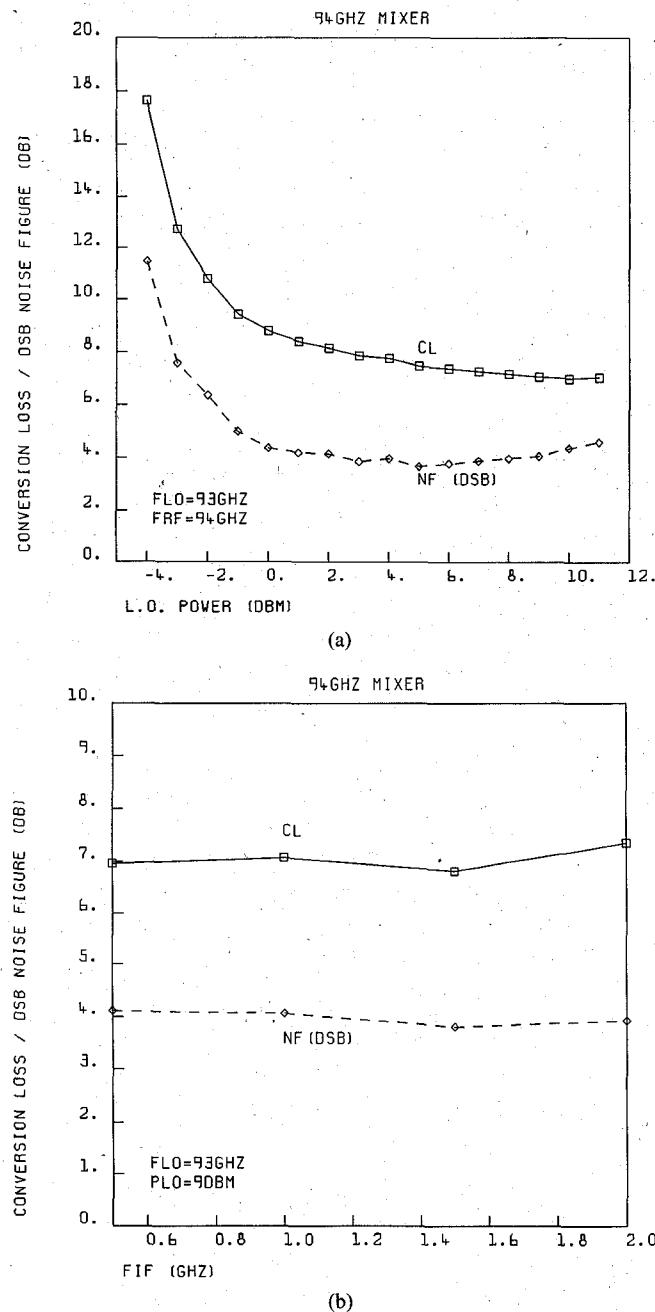

A monolithic 94 GHz mixer was reported in [13]. Fig. 14 shows the mixer circuit. The DSB noise figure and the conversion loss versus LO power and IF frequency are

Fig. 12. *V*-band mixer.

Fig. 13. DSB noise figure and conversion loss versus (a) LO power and (b) IF frequency for the mixer from Fig. 12.

Fig. 14. *W*-band mixer.

Fig. 15. DSB noise figure and conversion loss versus (a) LO power and (b) IF frequency for the mixer from Fig. 14.

represented in Fig. 15. A DSB noise figure of 4 dB associated with a conversion loss of 7.5 dB has been measured in self bias operation. In this case the LO power is 5 dBm at 93 GHz. The IF frequency is 1 GHz. The Schottky diode area is  $0.3 \times 5 \mu\text{m}^2$ . The chip size is  $2 \times 2 \text{ mm}^2$ . This mixer shows a very low LO power request.

## V. CONCLUSION

For the design of monolithic Schottky diode mixers a large signal equivalent circuit of the diode based on the technological parameters was developed. This model was implemented in a harmonic balance CAD software for analyzing the mixer circuit. Several mixers in the millimeter-wave frequency range have been designed. The ex-

perimental results are in good agreement with the design goals: low noise and conversion loss, minimum LO power request. The presented results are all obtained after the first pass design and prove the validity of the diode equivalent circuit and the design concept. Furthermore the design method is directly applicable to investigate the influence of the technological parameters on the mixer performances. Especially it is possible to predict the mixer performances for microwave applications using a technology without  $n^+$  buried layer.

## ACKNOWLEDGMENT

The authors would like to thank H. Kuhrmann for his assistance.

## REFERENCES

- [1] B. Adelseck and A. Colquhoun, "A monolithic integrated 35 GHz receiver employing a Schottky diode mixer and a MESFET IF amplifier," in *Proc. Gads IC Symp.*, Portland, OR, 1987, pp. 151-154.

- [2] B. Adelseck, A. Colquhoun, J.-M. Dieudonné, G. Ebert, K.-E. Schmegner, W. Schwab, and J. Selders, "A monolithic 60 GHz diode mixer and IF amplifier in compatible technology," *IEEE Trans. Microwave Theory Tech.*, vol. 37, pp. 2142-2147, Dec. 1989.

- [3] R. A. Pucel, H. H. Hans, and H. Statz, "Signal and noise properties of gallium arsenide microwave field effect transistors," *Advances in Electronics and Electronic Physics*, vol. 38, New York: Academic Press, 1975.

- [4] T. Takada, K. Jokoyama, M. Ida, and T. Sudo, "A MESFET variable-capacitance model for GaAs integrated circuit simulation," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 719-723, May 1982.

- [5] H. H. Berger, "Models for contacts to planar devices," *Solid-State Electron.*, vol. 15, pp. 145-158, 1972.

- [6] J. L. Heaton, "Analytical model speeds planar-mixer diode design," *Microwaves and RF*, pp. 102-110, Sept. 1984.

- [7] S. M. Sze, *Physics of Semiconductor Devices*, 2nd Ed. New York: Wiley.

- [8] H. Fukui, "Determination of the basic Device Parameters of a GaAs MESFET," *Bell Syst. Tech. J.*, vol. 58, no. 3, Mar. 1979.

- [9] D. N. Held and A. R. Kerr, "Conversion loss and noise of microwave and millimeter-wave mixers: Part-I-Theory," *IEEE Trans. Microwave Theory Tech.*, vol. 26, no. 2, pp. 45-55, Feb. 1978.

- [10] S. A. Maas, *Microwave Mixers*. Norwood, MA: Artech House, 1986.

- [11] G. M. Hegazi, A. Telenski, and K. Sigfrid Yngvesson, "Limitations of microwave and millimeter-wave mixers due to excess noise," *IEEE Trans. Microwave Theory Tech.*, vol. 33, no. 12, pp. 1404-1408, Dec. 1985.

- [12] J.-M. Dieudonné, K.-E. Schmegner, B. Adelseck, W. Schwab, A. Colquhoun, and J. Selders, "Conception et réalisation d'un mélangeur monolithique à 60 GHz," *Annales des Télécommunications*, vol. 45, no. 5-6, 1990.

- [13] B. Adelseck, J.-M. Dieudonné, K.-E. Schmegner, A. Colquhoun, G. Ebert, and J. Selders, "A monolithic 94 GHz balanced mixer," in *IEEE 1990 Microwave and Millimeter-Wave Monolithic Circuits Symp.*, Dallas, pp. 111-114.

Jean-Marie Dieudonné was born in 1960 in Dieuze, France. He received the Ingénieur degree from the Ecole Nationale Supérieure de l'Électronique et des ses Applications, Cergy, France, in 1983 and the Docteur-Ingénieur degree from the Paul Sabatier University, Toulouse, France, in 1986.

From 1983 to 1986 he worked at the Laboratoire d'Automatique et d'Analyse des Systèmes of the Centre National de la Recherche Scientifique, Toulouse, on GaAlAs/GaAs field-effect transis-

tors. In 1986 he joined the High Frequency Institute of the Technical University of Darmstadt, West Germany, where he was involved in microwave circuit design. Since 1988, he has been with the Telefunken Systemtechnik in Ulm, West Germany. His current activities concern the development of millimeter-wave monolithic integrated circuits.

**Bernd Adelseck** (S'90-M'84) received the Dipl.-Ing. degree in electrical engineering in 1976 from the RWTH Aachen, West Germany. Since then he has worked with Telefunken Systemtechnik, former AEG Radio and Radar Systems Division, Ulm, West Germany. He was involved in the development of planar integrated millimeter-wave circuits in image line, finline and microstrip techniques. Since 1985 he has been responsible for the development of monolithic millimeter-wave IC's. At present he is manager of the development department of planar high frequency circuits at Telefunken Systemtechnik (German Aerospace).

**Karl-Ernst Schmegner** (M'88) was born on February 28, 1950, in Kirchgellersen, Germany. He received the Dipl.-Ing. degree in electrical engineering from the University of Stuttgart, Germany and the Dr.-Ing. in 1983 from the RWTH Aachen, Germany. In 1983, he joined the Radio and Radars System Division of Telefunken in Ulm, Germany. He has been working on power generation at millimeter-wave frequencies with solid-state devices. His current activities concern the development of micro- and millimeter-wave monolithic integrated circuits. He is responsible for the measurement techniques of millimeter-wave MMIC's.

**Rainer Rittmeyer** was born on September 18, 1956, in Neu-Ulm, Germany. He received the Dipl.-Ing. degree in communications engineering from the Fachhochschule Ulm, in 1981.

Since 1981 he has been with the Telefunken Systemtechnik Radio and Radar Group, Ulm, Germany.

**Alexander Colquhoun** (S'73-M'76) was born in Jamestown, Scotland, on January 5, 1951. He received the B.Sc. degree in physics from the University of Liverpool, England in 1972 and the Ph.D. degree in electronic engineering from the University of Newcastle on Tyne, England in 1975.

In 1978 he joined Telefunken electronic, Heilbronn, Germany. From 1984 until 1991 he was manager of the department for the development of GaAs components with responsibility for both discrete and integrated components. In January 1992 he moved to the Daimler-Benz research center in Ulm, Germany where he is now responsible for GaAs foundry activities. His interests have covered III-V-epitaxy, including LPE, VPE and MOCVD, Gunn devices, GaAs MESFETs, HEMTs and mixer diodes for mm-wave applications. In recent years he has been actively involved in the development of analog GaAs MMICs for mm-wave applications.

Dr. Colquhoun is author or co-author of more than 30 publications, holds a number of relevant patents.